| Data Inputs |

There is 1 streaming input, from the Threshold Logic module.

|

| Configuration and Control Inputs |

Note that the Selectors, Max window length, and saturated-pulse timestamp offset are set during initialization1 at the start of running and are expected to remain the same after that, but they can be changed at any time if needed. |

| Output |

There is 1 streaming output, which goes to the Trigger Logic (TrL) module.

|

| Internal Registers |

This module requires some information to be retained from one time step to the next. It will

be stored in the following internal registers. These registers are not visible or accessible

from outside the module. They are mentioned and named here in order to simplify the detailed

description of the module's functionality given below.

|

| Error bits |

The module detects and reports several possible erroneous conditions via a register read. The value read out consists of 16 bits; the most-significant bits are unused.

|

| Functionality |

Brief functional description:

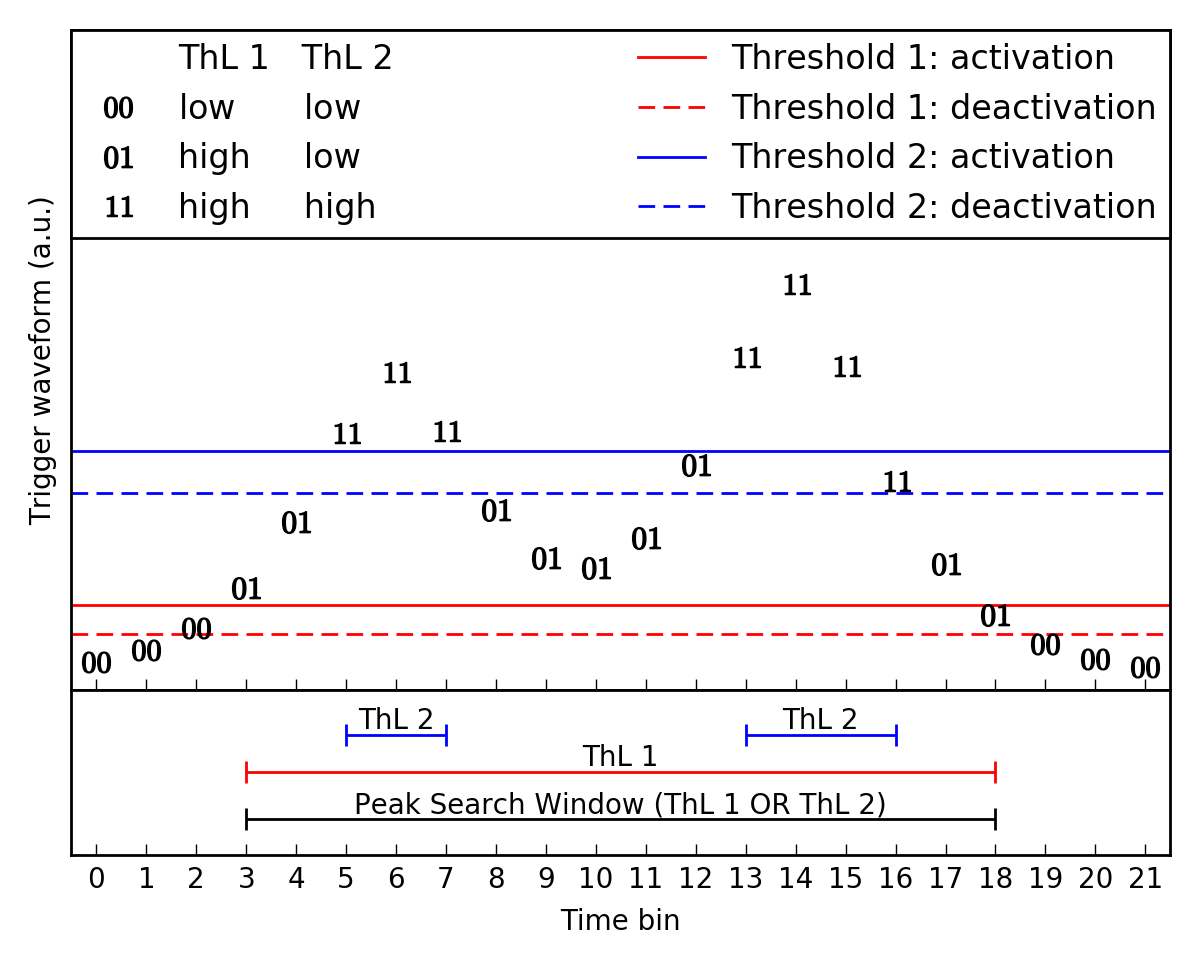

Each PS submodule does a number of things. It defines a "peak search window", which will be used to construct a set of "trigger primitives". The trigger primitives consist of the peak amplitude and peak timestamp of the input trigger waveform as well as a "trigger word" that contains the state of all 8 input threshold logic bits during the peak search window and at the trigger waveform peak. It also handles "saturated pulses", which are a difficult but frequent occurence. Finally, the trigger primitives are sent on to the TrL module, which makes the final L1 trigger decision. Figure 1 shows an example trigger waveform input (the same as used in Figure 1 on the ThL module design page) from FIR submodule 0. We will use and expand on this example through the rest of this page. In this example, we assume that ThL Selectors 1 and 2 are set to 0 (associated with FIR submodule 0) while all the other ThL Selectors are set to other values. This figure shows, in this example, how the peak search window is defined from the input threshold logic bits ThL 1 and ThL 2.

Figure 1: This figure shows the same input as used in the ThL design page with a pileup event for FIR 0. In this case only ThL 1 and ThL 2 are used for this trigger waveform. Note that the activation and deactivation lines are not used directly in the PS module, only the values of the ThL 1 and ThL 2 results, and the value of the trigger waveform which contains the information needed. Peak Search Window definitionThe peak search window is the time during which the trigger waveform is above the lowest of the associated thresholds described in the ThL module, where said association is defined by the Threshold Logic Selectors. In a little more detail, the Peak Search Window is defined using the 8 ThL bits received from the ThL module as well as the Threshold Logic Selectors described in the Configuration and Control Inputs. That is, for peak search submodule \(n\), Threshold Logic Selectors \(s_i\), and ThL bits \(t_i\), the peak search window is any contiguous block of time in which the following "peak search window bit" is TRUE: \[\operatorname*{OR}_{i=0}^{7} ((s_i == n) \operatorname{AND} t_i),\] where \(\operatorname*{OR}_{i=0}^{7}\) is the logical OR of all eight terms, and \(\operatorname{AND}\) is the logical AND operator. The peak search window begins when this expression becomes TRUE, and ends again when it becomes FALSE once again. Note that the "$t_0$" internal register will be set to the current timestamp at the moment the peak search window begins. Although the peak search window is not reported in the output, it is used to define the trigger primitives (peak amplitude, peak timestamp, and trigger word), which are described in the next section. Continuing the example from Figure 1, we assume that ThL Selectors 1 and 2 are set to this FIR input while all the other ThL Selectors are set to other FIR inputs. That is, this trigger waveform has only the two thresholds (and corresponding ThL bits) shown in Figure 1. Then, the peak search window for this submodule is defined by the logical OR of both of the two ThL bits. In Figure 1, ThL 2 has the value 1 during time bins 5-7 and again during time bins 13-16, and ThL 1 has the value 1 during time bins 3-18, and so the peak search window in this example extends from time bin 3 to time bin 18, inclusive. Construction of the trigger primitivesA set of trigger primitives consists of the peak amplitude, peak timestamp, and the trigger word, which records the status of the threshold logic bits during the peak search window and at the trigger waveform peak. Each PS submodule searches for the peak amplitude within its peak search window. It records the peak amplitude and the timestamp at which that peak amplitude occurred. These pieces of information for our example are shown in Figure 2 and Table 1. In our example, the peak amplitude is 145 and the peak timestamp is 14. Each submodule also constructs the trigger word based on the input threshold logic bits. The first 8 bits of the trigger word are just the values of the 8 threshold logic bits at the time of the peak. The second 8 bits of the trigger word indicate whether each threshold was exceeded at any time during the peak search window. More precise details of how each of these pieces of information is constructed are given below in the step-by-step description. Table 1 makes explicit, in our example, exactly how the trigger word is constructed. Note that, although the peak search window is defined only by ThL 1 and ThL 2 (due to the values of the threshold logic Selectors), all of the threshold logic bits play a role in determining the trigger word. In particular, ThL 1, 2, 5, and 6 are all 1 at the peak, in time bin 14, and so the first 8 bits of the trigger word are 11001100. Additionally, ThL 7 and 8 are both 1 at some point during the peak search window, while ThL 3 is only 1 outside the peak search window and ThL 4 is never 1 at all. So, the second 8 bits of the trigger word are 11001111. Once the peak search window ends, the peak amplitude, peak time, and trigger word are sent to the TrL module, which makes the L1 trigger decision and sends everything on to the L1 FIFO. Handling of saturated pulsesSome scattering events in our detectors are energetic enough that the transition edge sensors become fully normal conducting and remain so for some time. This produces a pulse that has a markedly different shape than lower-energy pulses, a "saturated pulse". The effect, from the trigger perspective, is that the trigger waveform will rise up to some maximum amplitude and then remain there, nearly flat, for an extended length of time. Such a flat-topped trigger waveform does not have a unique peak. The actual maximum amplitude will occur at some random point on this flat top (determined by the noise and the fine details of the pulse shape) rather than at the beginning of the flat top. Because of this, the "peak timestamp" reported by the PS module is unlikely be aligned in a consistent fashion with the rising edge of the pulse. This means that the L2 trigger will not be able to correctly align the readout window with the rising edge of the pulse. Luckily, for such a high-amplitude pulse, the time between the beginning of the peak search window (when the trigger waveform first rises above the lowest threshold) and the timestamp needed for correctly placing the readout window is more or less constant. In order to properly handle this case, the PS submodules have two additional configuration inputs. The first is a maximum length \(t_\text{max}\) for the peak search window. If the window is below this maximum length, then the pulse is treated as a normal pulse, but if the window is longer than \(t_\text{max}\) then the pulse is treated as a saturated pulse. The second configuration input is a timestamp offset \(\Delta t_\text{sat}\). When a saturated pulse is detected, then this offset \(\Delta t_\text{sat}\) is added to the timestamp at the beginning of the peak search window \(t_0\), and that sum, \(\Delta t_\text{sat} + t_0\) is the reported peak timestamp in place of the timestamp of the actual peak. To sum up, \(t_\text{max}\) is used to identify saturated pulses, and \(\Delta t_\text{sat}\) is used, along with the value in the \(t_0\) internal register, to report a useful timestamp in the case of saturated pulses. Note: there is no explicit identification of saturated pulses in the trigger primitives, although the reported peak amplitude will be very large for saturated pulses. More detailed description (including data transfer information):Step-by-step:This describes the functionality of one PS submodule. All 4 PS submodules work identically and in parallel.

Start of peak search window steps:

During peak search window steps:

End of peak search window steps:

Reset signal:When the reset signal is asserted,

When the reset signal is deasserted,

|

| Notes |

|

| Testing Plan |